電纜故障測試儀脈沖法原理

發(fā)布時(shí)間:2016-06-17 09:00:00

瀏覽次數:4861

? 華意電力是一家專(zhuān)業(yè)研發(fā)生產(chǎn)電纜故障測試儀的廠(chǎng)家��,本公司生產(chǎn)的電纜故障測試儀在行業(yè)內都廣受好評�,以打造最具權威的“電纜故障測試儀“高壓設備供應商而努力����。電纜是通信�����、測試等系統信號傳輸的重要載體��,隨著(zhù)電纜數量的增多及運行時(shí)間的延長(cháng)�,電纜也越來(lái)越頻繁地發(fā)生故障���。電纜線(xiàn)路的隱蔽性及測試設備的局限性�����,使電纜故障的查找非常困難�。本文設計了一種以嵌入式微處理器Nios為核心的電纜故障檢測儀�,應用A/D器件和FPGA組成可變頻率的高速數據采集系統�����,利用低壓脈沖反射法原理來(lái)實(shí)現線(xiàn)纜的斷路���、短路�����、斷路點(diǎn)�、短路點(diǎn)的檢測與定位��。該儀器可廣泛應用于通信維護�����、工程施工和綜合布線(xiàn)��,對市話(huà)電纜����、同軸電纜等各種線(xiàn)纜進(jìn)行測試和障礙維護�。

1 系統總體結構

? 利用低壓脈沖反射法檢測電纜故障����。主要原理是:向電纜發(fā)送一個(gè)電壓脈沖�����,當發(fā)射脈沖在傳輸線(xiàn)上遇到故障時(shí)�,由于故障點(diǎn)阻抗不匹配�,產(chǎn)生反向脈沖����,通過(guò)計算二者的時(shí)間差△T�,并分析反射脈沖的特性來(lái)進(jìn)行故障的定性與定位��。該方法適用于斷線(xiàn)�、接觸不良��、低電阻或短路故障的測試���。

故障點(diǎn)距離L為:L=V·△T/2����。式中����,V是脈沖在電纜中的傳播速度���。根據反向脈沖的極性可判斷故障性質(zhì):斷線(xiàn)或接觸不良引起的反向脈沖為正���,低電阻或短路故障引起的反向脈沖為負���。

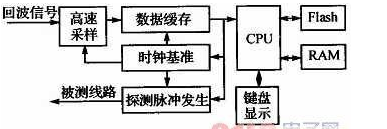

? 電纜故障測試儀是一個(gè)便攜式電纜故障檢測設備��,可利用現代電子技術(shù)(如高速A/D技術(shù)�����、異步FIFO技術(shù)�、現場(chǎng)可編程邏輯陣列FPGA等)來(lái)提高集成度和靈活性����。系統總體結構如圖1所示����。

? 脈沖發(fā)生電路產(chǎn)生探測脈沖�����,高速的A/D轉換器對脈沖及其反射回波信號進(jìn)行采樣���,使用異步FIFO作為A/D采樣數據的緩存��。軟核Nios作為系統核心��,控制檢測任務(wù)的啟動(dòng)和結束�、脈沖發(fā)送接收模式的選擇�、A/D采樣數據的處理計算����、故障性質(zhì)和位置的判斷及顯示等��。其中�,軟核處理器和邏輯功能都是在現場(chǎng)可編程邏輯器件中編程實(shí)現的�。

2 功能及性能指標

短路測試:檢測電纜芯線(xiàn)之間是否有不必要的連接及其位置����。

斷路測試:檢測電纜中某芯線(xiàn)是否斷路及其位置���。

顯示:顯示測試結果�����,即測量中開(kāi)路及短路的位置����。

測量范圍:2~1000 m����。

測試精度:可選擇2 m和10 m兩種精度����。

脈沖振幅:負載開(kāi)路5 V�����。

脈沖寬度:20 ns�,100 ns��。

最大采樣速率:100 MHz����。

波形記錄長(cháng)度:1024點(diǎn)���。?

3.1 微處理器系統

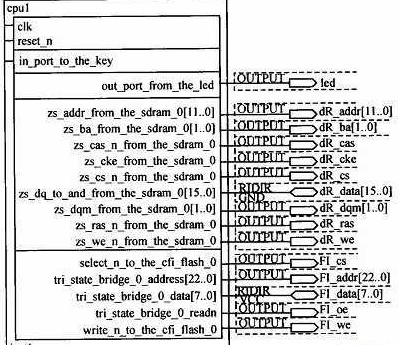

簡(jiǎn)單來(lái)說(shuō)���,Nios是一種處理器的IP核�����,設計者可以將它放到FPGA中����。Nios軟核處理器是一種基干流水線(xiàn)的精簡(jiǎn)指令集通用微處理器�,時(shí)鐘信號頻率最高可達75 MHz���。采用Flash來(lái)存儲啟動(dòng)代碼和應用程序�,當系統復位或加電啟動(dòng)時(shí)�,Flash中的啟動(dòng)代碼將被執行���。采用SDRAM存儲應用程序的可執行代碼和數據�,為程序提供運行空間��。Nios軟核與Flash和SDRAM的連接在FPGA中的設計如圖2所示��。

3.2 探測脈沖的產(chǎn)生

? 故障檢測所用脈沖信號的寬度為20~100 ns�����,FPGA的工作時(shí)鐘可以達到200 MHz�����,在其中生成減法計數器可產(chǎn)生滿(mǎn)足脈寬要求的脈沖信號���。減法計數器產(chǎn)生脈沖的幅度受限于FPGA的工作電平����,對檢測來(lái)說(shuō)是不夠的�,因此從FPGA中出來(lái)的方波脈沖還要經(jīng)過(guò)放大�����,才可以耦合到被檢測線(xiàn)纜中去�����。脈沖信號調理電路如圖3所示�����。SN74LVC4245A用作電平轉換���。sta和pulse_input均來(lái)自FPGA���。

3.3 A/D轉換電路

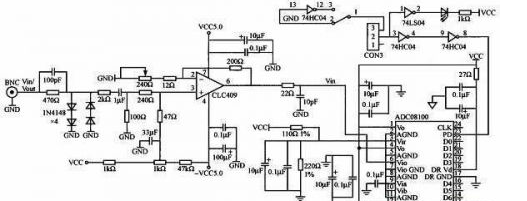

檢測脈沖的寬度為20~100 ns��,相應的數據采樣率在20 MHz和100 MHz之間變化�,一般的A/D芯片很難滿(mǎn)足采樣的要求���,而用多片A/D芯片在成本和設計上都比較困難�����。這里選用美國NS公司的ADC08100�,其采樣速率為20~100 Msps��,此時(shí)采樣的功耗為1.3 mW/Msps����,采樣的功耗會(huì )隨著(zhù)采樣時(shí)鐘增加而增加��,但是采樣的特性不會(huì )受到影響��,因此在采樣率多樣的系統中一個(gè)芯片可以起到多個(gè)芯片的作用�。根據采樣速率的不同����,通過(guò)一個(gè)時(shí)鐘控制模塊產(chǎn)生相應的采樣時(shí)鐘信號��,使芯片工作在所要求的速率之下�����,既可以節約成本���,又可以簡(jiǎn)化設計�。ADC08 100和FPGA配合使用��,可以方便地改變采樣時(shí)鐘���,具有很大的靈活性�����。

A/D轉換電路如圖4所示�����。探測脈沖及回波信號需要轉換成適合A/D芯片電壓水平的信號后再進(jìn)行采樣��。脈沖在輸入運算放大器之前進(jìn)行了鉗位處理�,采用兩組倒置的二極管并聯(lián)����,避免脈沖過(guò)高而擊穿運算放大器�。

3.4 時(shí)鐘信號的產(chǎn)生

檢測脈沖的產(chǎn)生�����、ADC08100的采樣��,以及異步FIFO的數據緩存構成了一個(gè)高速A/D數據采集系統���。這對于各種信號的時(shí)間配合要求很高���,需要專(zhuān)門(mén)的時(shí)鐘單元來(lái)配合���,以使電路工作在正確的時(shí)序之下���。在FPGA中可方便地定制時(shí)鐘模塊來(lái)產(chǎn)生A/D采樣時(shí)鐘�����、異步存儲器的讀寫(xiě)時(shí)鐘�����,以及脈沖發(fā)生模塊的計數時(shí)鐘���。所有的時(shí)鐘都是由一個(gè)高速的時(shí)鐘來(lái)實(shí)現同步的�,并且整個(gè)系統是在同一個(gè)啟動(dòng)信號下同步運行的�,從而保證了采樣的時(shí)序要求�。

3.5 電源模塊

系統中既有模擬電路又有高速數字電路�����,使用電源種類(lèi)復雜����,存在+5 V��、+3.3 V��、+1.2 V�、-5 V等多種電源信號�����。在電路板設計制作中既要減小高頻數字信號對模擬信號的電磁干擾���,又要避免各種電源之間的干擾�,因此需合理規劃模塊布局及布線(xiàn)走向以提高信號穩定性�����。

4 軟件設計

軟件設計主要包括FPGA的開(kāi)發(fā)應用����、應用程序設計以及液晶顯示器的驅動(dòng)程序設計等�。

4.1 FPGA開(kāi)發(fā)應用

現場(chǎng)可編程邏輯器件FPGA(Field Programming Gate Array)具有高密度���、高速度��、低功耗���、功能強大等特點(diǎn)����。在此系統中采用了Altera公司的CycloneII系列器件來(lái)實(shí)現高速的數據采集���、存儲功能�����,是在QuartuslI 7.1軟件中使用硬件描述語(yǔ)言VHDL來(lái)設計完成的����。高密度可編程邏輯器件的設計流程包括:設計準備���、設計輸入�、設計處理和器件編程4個(gè)步驟���,以及相應的功能仿真(前仿真)�、時(shí)序仿真(后仿真)和器件測試3個(gè)設計驗證過(guò)程����。

本設計中�,主要包括Nios微處理器�����、脈沖發(fā)生��、高速時(shí)鐘以及高速數據存儲FIFO等模塊的設計�。

4.2 應用程序設計

應用程序控制檢測任務(wù)的啟動(dòng)和結束��、脈沖發(fā)送接收模式的選擇�、A/D采樣數據的處理計算�����、故障性質(zhì)和位置的判斷以及結果輸出等���。